# SEMICONDUCTOR TECHNICAL DATA

### FSP8103ASG

## **Current Mode PWM Controller with Frequency Shuffling**

#### **General Description**

FSP8103ASG integrates a PWM controller and high voltage power MOSFET of 650V/4A. FSP8103ASG has the features of very low standby power (<100mW) when AC power above 220Vac. It delivers up to 18W of output power over a wide voltage range of 85V to 265V ,and a peak output power of up to 20W.

FSP8103ASG offers complete protection coverage with Cycle-by-Cycle current limiting (OCP), over temperature protection (OTP), over load protection (OLP), and VCC under voltage lockout (UVLO) and over voltage protection (OVP).

## Typical Application

Offline AC/DC flyback converter for

- Switching AC/DC Power battery charge

- Digital cameras and camcorder adapter

- Set-top box power

- Auxiliary power supply for PC and server

- Open-frame SMPS

- PD fast charge

#### **Features**

- Low startup current

- Audio Noise Free Operation

- Burst Mode Control

- Frequency Shuffling Technology

- Compensation for ac-in

- Leading Edge Blanking

- Internal Synchronized Slope Compensation

- Good Protection Coverage With Auto

Self-Recovery: OCP, OLP, UVLO, OVP, OTP

#### **Package**

• 8-pin SOP8

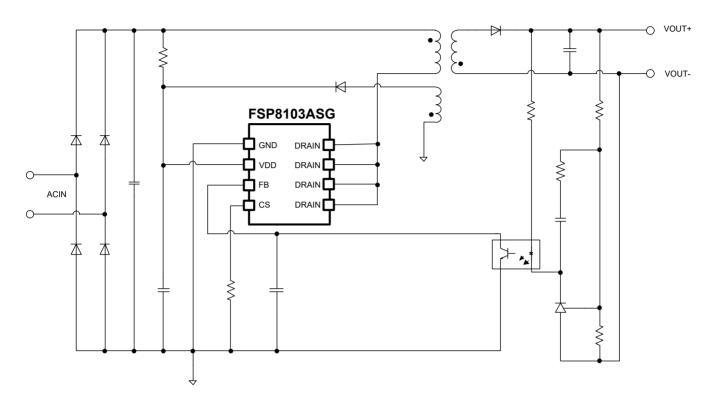

## **Typical Application Circuit**

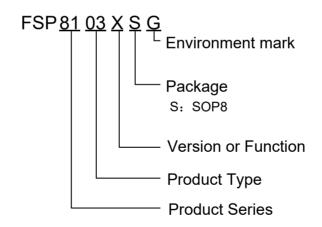

## **Selection Guide**

| product series | product description |

|----------------|---------------------|

| FSP8103ASG     | Package: SOP8       |

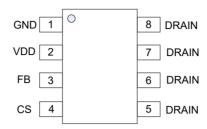

## **Pin Configuration& Pin Assignment**

SOP8

## **PIN Assignments**

| Symbol | ol Pin Num. Functio |                           | Description      |

|--------|---------------------|---------------------------|------------------|

| GND    | 1                   | Ground Ground             |                  |

| VDD    | 2                   | Power Supply Power Supply |                  |

| FB     | 3                   | Input                     | Feedback         |

| CS     | 4                   | Input                     | Current Sense    |

| DRAIN  | 5,6,7,8             | Input                     | Drain of the MOS |

## **Block Diagram**

2025. 02. 25

## FSP8103ASG

## **Absolute Maximum Ratings**

| Parameter                                          | Range        | Unit |

|----------------------------------------------------|--------------|------|

| DRAIN Input Voltage                                | 650          | V    |

| VDD Input Voltage                                  | -0.3~30      | V    |

| VDD Input Current                                  | 0~5          | mA   |

| CS, FB Input Voltage                               | -0.3~7       | V    |

| Thermal resistance (Junction to air) $\theta_{JA}$ | 136          | °C/W |

| Continuous Total Power Dissipation P <sub>D</sub>  | 0.92         | W    |

| Operating ambient temperature :T <sub>A</sub>      | -20~85       | °C   |

| Storage Temperature Tstg                           | -55~150      | °C   |

| Maximum junction temperature T <sub>J</sub>        | -40~150      | °C   |

| Welding Temperature                                | +260 (10sec) | °C   |

## **Recommended Operating Condition**

| Parameter                     | Range  | Unit |

|-------------------------------|--------|------|

| VDD Input Voltage             | 10~30  | V    |

| Operating Ambient Temperature | -20~85 | °C   |

## **Electrical Characteristics** (TA = 25 °C, VDD=16V, if not otherwise noted)

| Symbol                   | Parameter                                | Test Conditions                                        | Min | Тур. | Max | Unit |  |

|--------------------------|------------------------------------------|--------------------------------------------------------|-----|------|-----|------|--|

| Supply Voltage (VDD)     |                                          |                                                        |     |      |     |      |  |

| Is                       | Start-Up Current Sourced from VDD Pin    | VDD= UVLO <sub>OFF</sub> -1V, Current flowing into VDD | -   | 5    | 20  | μA   |  |

| Io                       | Operation Current                        | V <sub>FB</sub> =3V                                    | -   | 1    | 2   | mA   |  |

| UVLO <sub>ON</sub>       | Under-Voltage Lockout Voltage of VDD Pin |                                                        | 8   | 9    | 10  | V    |  |

| UVLO <sub>OFF</sub>      | Start-Up Voltage of VDD Pin              |                                                        | 14  | 15   | 16  | V    |  |

| VDD_Clamp                | Clamp Voltage of VDD Pin                 | I <sub>VDD</sub> = 5 mA                                | 32  | 35   | 37  | V    |  |

| OVP <sub>ON</sub>        | OVP Voltage of VDD Pin                   |                                                        | 28  | 30   | 32  | V    |  |

| OVP <sub>OFF</sub>       | OVP off Voltage of VDD Pin               |                                                        | 24  | 26   | 28  | V    |  |

| OTP                      |                                          |                                                        |     | 155  | 165 | °C   |  |

| Feedback(FE              | 3)                                       |                                                        | •   |      |     | •    |  |

| AV <sub>SENSE</sub>      | PWM Input Gain                           |                                                        | -   | 2    | -   | V/V  |  |

| Maximum duty cycle       | Maximum Duty Cycle                       | VDD=16V, V <sub>FB</sub> =3V, V <sub>CS</sub> =0V      | 75  | 80   | 85  | %    |  |

| V <sub>FB_Open</sub>     | FB pin Open Loop Voltage                 |                                                        | 4.5 | 5    | 5.5 | V    |  |

| I <sub>FB_Short</sub>    | FB pin short circuit current             |                                                        | -   | 0.4  | -   | mA   |  |

| V <sub>REF_GREEN</sub>   | The threshold enter green mode           |                                                        | -   | 1.8  | -   | V    |  |

| V <sub>REF_BURST_H</sub> | The threshold exit burst mode            |                                                        | -   | 1.1  | -   | V    |  |

| V <sub>REF_BURST_L</sub> | The threshold enter burst mode           |                                                        | -   | 1    | -   | V    |  |

#### FSP8103ASG

|                   | Dower Limiting ED Throphold                       |                               |     |      |     |     |

|-------------------|---------------------------------------------------|-------------------------------|-----|------|-----|-----|

| $V_{TH\_PL}$      | Power Limiting FB Threshold Voltage               |                               | -   | 3.5  | -   | V   |

| $T_D\_PL$         | Power limiting Debounce Time                      |                               | 30  | 38   | 46  | mS  |

| Current Sens      | se Input(CS)                                      |                               |     |      |     |     |

| T_blanking        | Leading edge blanking time                        |                               | -   | 220  | -   | nS  |

| T <sub>D_OC</sub> | Over Current Detection and Control Delay          |                               | -   | 120  | -   | nS  |

| $V_{TH\_OC}$      | Over Current Threshold Voltage at zero Duty Cycle | FB=3.3V                       | 0.7 | 0.75 | 0.8 | V   |

| Oscillator        |                                                   |                               |     |      |     |     |

| Fosc              | Normal Oscillation Frequency                      | VDD=16V,FB=3V,CS=0V           | 60  | 67.5 | 75  | KHz |

| ∆f_Temp           | Frequency Temperature Stability                   | VDD = 16V,                    |     | 5    |     | %   |

|                   |                                                   | TA -20℃ to 140℃               |     |      |     | 70  |

| Δf_VDD            | Frequency Voltage Stability                       | VDD = 9-25V,                  |     | 5    |     | %   |

| Δf_OSC            | Frequency Modulation range /Base frequency        |                               | -   | ±6   | -   | %   |

| F_shuffling       | Shuffling Frequency                               |                               | -   | 32   | -   | Hz  |

| F_Burst           | Burst Mode Base Frequency                         |                               | -   | 25   | -   | KHz |

| Drain of the      | MOSFET (DRAIN)                                    |                               |     |      |     |     |

| BVdss             | Drain-Source Voltage                              | Vgs=0                         | 650 | -    | -   | V   |

| Ron               | Static Drain-Source On-Resistance                 | V <sub>GS</sub> =10V, Id=2.5A | -   | -    | 3   | Ω   |

| I <sub>D</sub>    | Continuous drain current                          |                               | -   | 4    | -   | Α   |

|                   |                                                   |                               | 1   | 1    | 1   | 1   |

## **Operation Description**

The FSP8103ASG is a low power off-line SMPS Switcher optimized for off-line flyback converter applications in 18W power range. The 'Extended burst mode' control greatly reduces the standby power consumption and helps the design easily to meet the international power conservation requirements.

#### **Startup Current and Start up Control**

Startup current of FSP8103ASG is designed to be very low so that VCC could be charged up above UVLO threshold level and device starts up quickly. A large value startup resistor can therefore be used to minimize the power loss yet provides reliable startup in application. For a typical AC/DC adaptor with universal input range design, a 2 M $\Omega$ , 1/8 W startup resistor could be used together with a VCC capacitor to provide a fast start up and low power dissipation design solution.

#### Frequency shuffling for EMI improvement

Revision No: 0

The frequency Shuffling/jittering (switching frequency modulation) is implemented in FSP8103ASG. The oscillation frequency is modulated with a random source so that the tone energy is spread out. The spread spectrum minimizes

# 73

#### FSP8103ASG

the conduction band EMI and therefore reduces system design challenge.

#### **Current Sensing and Leading Edge Blanking**

Cycle-by-Cycle current limiting is offered in FSP8103ASG current mode PWM control. The switch current is detected by a sense resistor into the sense pin. Each time the power MOSFET is switched on, a turn on spike will inevitably occur at the sense resistor. To avoid fault trigger, a 220ns leading-edge blanking time is built in. Conventional RC filtering can therefore be omitted. During this blanking period, the current-limit comparator is disabled and cannot switch off the gate driver.

#### **Extended Burst Mode Operation**

At zero load or light load condition, majority of the power dissipation in a switching mode power supply is from switching loss on the MOSFET transistor, the core loss of the transformer and the loss on the snubber circuit. The magnitude of power loss is in proportion to the switching frequency. Lower switching frequency leads to the reduction on the power loss and thus conserves the energy.

The switching frequency is internally adjusted at no load or light load condition. The switch frequency reduces at light/no load condition to improve the conversion efficiency. At light load or no load condition, the FB input drops below burst mode threshold level and device enters Burst Mode control. The Gate drive output switches only when VCC voltage drops below a preset level and FB input is active to output an on state. Otherwise the gate drive remains at off state to minimize the switching loss and reduces the standby power consumption to the greatest extend. The nature of high frequency switching also reduces the audio noise at any loading conditions.

#### **Protection Controls**

Good power supply system reliability is achieved with its rich protection features including Cycle-by-Cycle current limiting (OCP), Over Load Protection (OLP), CS short protection, CS floating protection, over voltage protection (OVP), and Under Voltage Lockout on VCC (UVLO).

The OCP is line voltage compensated to achieve constant output power limit over the universal input voltage range.

At overload condition, When FB input exceeds power limit threshold value for more than  $T_{D\_PL}$ , control circuit reacts to shut down the Input power MOSFET. Similarly, control circuit reacts to shut down the switcher. Switcher restarts when VCC voltage drops below UVLO limit.

Revision No: 0

6/7

## FSP8103ASG

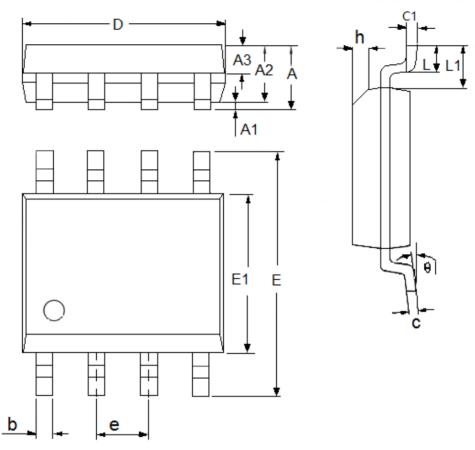

## **Packaging Information**

Packaging Type: SOP8

| DIM   |           | neters | Inch   | es     |

|-------|-----------|--------|--------|--------|

| DIIVI | Min       | Max    | Min    | Max    |

| Α     | 1.3       | 1.8    | 0.0512 | 0.0709 |

| A1    | 0.05      | 0.25   | 0.002  | 0.0098 |

| A2    | 1.25      | 1.65   | 0.0492 | 0.065  |

| A3    | 0.5       | 0.7    | 0.0197 | 0.0276 |

| b     | 0.3       | 0.51   | 0.0118 | 0.0201 |

| С     | 0.17      | 0.25   | 0.0067 | 0.0098 |

| D     | 4.7       | 5.1    | 0.185  | 0.2008 |

| Е     | 5.8       | 6.2    | 0.2283 | 0.2441 |

| E1    | 3.8       | 4      | 0.1496 | 0.1575 |

| е     | 1.27(     | TYP)   | 0.05(7 | YP)    |

| h     | 0.25      | 0.5    | 0.0098 | 0.0197 |

| L     | 0.4       | 1.27   | 0.0157 | 0.05   |

| L1    | 1.04(TYP) |        | 0.0409 | (TYP)  |

| θ     | 0         | 8°     | 0      | 8°     |

| c1    | 0.25(TYP) |        | 0.0098 | (TYP)  |