# SEMICONDUCTOR TECHNICAL DATA

#### FTD1670

## 60V, 1.2A, 480kHz Non-synchronous Buck Converter

## **General Description**

The FTD1670 is a monolithic, step-down, switch mode converter with a built-in power MOSFET. It achieves a 1.2A peak-output current over input supply 10V-60V with excellent load and line regulation. Current-mode operation provides a fast transient response and eases loop stabilization. Fault condition protections include cycle-by-cycle current limiting and thermal shutdown.

The FTD1670 requires a minimal number of readily-available external components.

The FTD1670 is available in a ESOP-8 package.

#### **Features**

- 1.2A Peak Output Current

- 0.7Ω Internal Power MOSFET

- Stable with Low-ESR Ceramic Output Capacitors

- Up to 91% Efficiency

- 0.1μA Shutdown Mode

- Fixed 480kHz Frequency

- Thermal Shutdown

- Cycle-by-Cycle Over-Current Protection

- 11V to 60V Operating Input Range

- Max duty 90%

- Available in a ESOP-8 Package

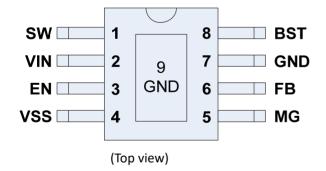

## **Pin Configurations**

## **Applications**

- Power Meters

- Distributed Power Systems

- Battery Chargers

- Pre-Regulator for Linear Regulators

- WLED Drivers

# **Pin Description**

| Pin Number | Pin Name | Description                                                                                               |

|------------|----------|-----------------------------------------------------------------------------------------------------------|

| 1          | CVA      | Power Switching Output. It is the Drain of the N-Channel power MOSFET to supply power to                  |

| 1          | SW       | the output LC filter.                                                                                     |

| 2          | VIN      | Supply Voltage. The FTD1670 operates from a 10V-to-60V unregulated input. Requires C1 to                  |

| 2          | VIIN     | prevent large voltage spikes from appearing at the input.                                                 |

| 2          | - FNI    | On/Off. Pull EN above 1.35V to turn the device ON. For automatic enable, connect to $V_{\text{IN}}$ using |

| 3          | EN       | a $1M\Omega$ resistor.                                                                                    |

| 4          | VSS      | Source of the MOS                                                                                         |

| 5          | MG       | Gate of the MOS                                                                                           |

|            |          | Feedback. Sets the output voltage. Connect to the tap of an external resistor divider from the            |

| 6          | FB       | output to GND. The frequency foldback comparator lowers the oscillator frequency when the                 |

|            |          | FB voltage is below 300mV to prevent current-limit runaway during a short-circuit fault.                  |

|            |          | Bootstrap. Connect a capacitor between the SW and BS pins to form a floating supply across                |

| 7          | BST      | the power switch driver. This capacitor drives the power switch's gate above the supply                   |

|            |          | voltage.                                                                                                  |

|            |          | Ground. Voltage reference for the regulated output voltage. Requires special layout                       |

| 8          | GND      | considerations. Isolate this node from the D1 to C1 ground path to prevent switching current              |

|            |          | spikes from inducing.                                                                                     |

# **Ordering Information**

|                | FTD1670 | $\frac{\Box}{\Box}$ |                           |

|----------------|---------|---------------------|---------------------------|

| Circuit Type — |         |                     | — Packing:<br>Blank: Tube |

| Package        |         |                     | R: Tape and Reel          |

2023. 12. 01 Revision No : 0 **First Silicon** 2/7

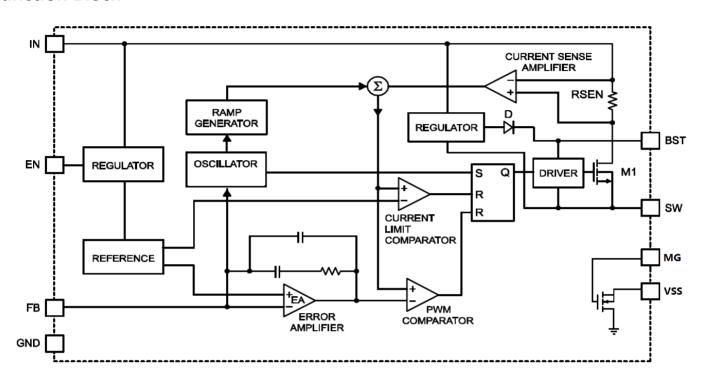

#### **Function Block**

Figure 1 Function Block Diagram of FTD1670

## Absolute Maximum Ratings (Note1)

Revision No: 0

| Symbol           | Parameter                                       | Rating                                                       | Unit       |

|------------------|-------------------------------------------------|--------------------------------------------------------------|------------|

| Vin              | VIN Supply Voltage(VIN to Gnd)                  | -0.3 ~ 60                                                    | V          |

| $V_{SW}$         | SW to GND Voltage                               | -0.3 to V <sub>IN</sub> +0.3                                 | V          |

| V <sub>BS</sub>  | BS to GND Voltage                               | BS to GND Voltage V <sub>SW</sub> - 0.3 ~ V <sub>SW</sub> +6 |            |

|                  | All Other Pins                                  | -0.3 ~ 6                                                     | V          |

| P <sub>D</sub>   | Power Dissipation                               | Internally Limited                                           | W          |

| Tj               | Junction Temperature                            | 150                                                          | $^{\circ}$ |

| T <sub>STG</sub> | Storage Temperature                             | -65 ~ 150                                                    | °C         |

| T <sub>SDR</sub> | Maximum Lead Soldering Temperature (10 Seconds) | 260                                                          | $^{\circ}$ |

Note1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Thermal Characteristics**

| Symbol | Parameter                                           | Typical Value | Unit |

|--------|-----------------------------------------------------|---------------|------|

| θιΑ    | Junction-to-Ambient Resistance in free air (Note 2) | 60            | °C/W |

Note  $2:\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air.

# **Recommended Operation Conditions (Note3)**

| Symbol           | Parameter                | Range                                  | Unit       |

|------------------|--------------------------|----------------------------------------|------------|

| Vin              | VIN Supply Voltage       | 11 ~ 60                                | V          |

| V <sub>OUT</sub> | Converter Output Voltage | V <sub>FB</sub> ~ V <sub>IN</sub> *90% | ٧          |

|                  | Operating Junction Temp  | -40 ~ 125                              | $^{\circ}$ |

Note 3: Refer to the typical application circuit

#### **Electrical Characteristics**

Unless otherwise specified, these specifications apply over Vin=12V, Ven=3V and Ta = 25  $^{\circ}\text{C}$

Revision No: 0

| Symbol                | Parameter                                     | Test Conditions                         | Min   | Тур   | Max   | Unit |

|-----------------------|-----------------------------------------------|-----------------------------------------|-------|-------|-------|------|

| $V_{FB}$              | Feedback Voltage                              | $10V \leqslant V_{IN} \leqslant 60V$    | 0.792 | 0.812 | 0.832 | V    |

| I <sub>FB</sub>       | Feedback Current                              | VFB = 0.85V                             | -     | -     | 0.1   | μΑ   |

| R <sub>DS(ON)</sub>   | Switch-On Resistance                          |                                         | -     | 0.7   | -     | Ω    |

| I <sub>SW_LKG</sub>   | Switch Leakage                                | V <sub>EN</sub> =0V,V <sub>SW</sub> =0V | -     | -     | 1     | μΑ   |

| I <sub>LIM</sub>      | Current Limit                                 |                                         | -     | 1.65  | -     | А    |

| $f_{SW}$              | Oscillator Frequency                          | V <sub>FB</sub> =0.6V                   | 380   | 480   | 580   | kHz  |

| $f_{SW\_F}$           | Foldback Frequency                            | V <sub>FB</sub> =0V                     | -     | 120   | -     | KHz  |

| $D_{MAX}$             | Maximum Duty Cycle                            | V <sub>FB</sub> =0.6V                   | -     | 90    | -     | %    |

| $T_{ON}$              | Minimum ON-Time                               |                                         | -     | 100   | -     | ns   |

| $V_{UVLO_{R}}$        | Under-Voltage Lockout<br>Threshold, Rising    |                                         | -     | 7.5   | 8.5   | ٧    |

| $V_{UVLO_F}$          | Under-Voltage Lockout<br>Threshold, Falling   |                                         | -     | 7.1   | -     | ٧    |

| V <sub>UVLO_HYS</sub> | Under-Voltage Lockout<br>Threshold,Hysteresis |                                         | -     | 0.4   | -     | ٧    |

| $V_{EN_{R}}$          | EN Threshold, Rising                          |                                         | -     | 1.35  | -     | V    |

4/7

#### FTD1670

## 60V, 1.2A, 480kHz Non-synchronous Buck Converter

| V <sub>EN_F</sub>   | EN Threshold, Falling       |               | - | 1.17 | -    | V          |

|---------------------|-----------------------------|---------------|---|------|------|------------|

| V <sub>EN_HYS</sub> | EN Threshold, Hysteresis    |               | - | 180  | -    | mv         |

|                     | EN. 1 0                     | VEN=2V        | - | 3.1  | -    | μΑ         |

| I <sub>EN</sub>     | EN Input Current            | VEN=0V        | - | 0.1  | -    | μΑ         |

| Is                  | Supply Current (Shutdown)   | VEN=0V        | - | 0.1  | 1    | μΑ         |

| ΙQ                  | Supply Current (Quiescent)  | VEN=2V,VFB=1V | - | 0.73 | 0.85 | mA         |

| T <sub>SD</sub>     | Thermal Shutdown            |               | - | 165  | -    | $^{\circ}$ |

| T <sub>SD_HYS</sub> | Thermal Shutdown Hysteresis |               | - | 20   | -    | °C         |

#### (Hotswap FET)

| Symbol              | Parameter                        | Test Condition                                            | Min. | Тур. | Max. | Unit  |

|---------------------|----------------------------------|-----------------------------------------------------------|------|------|------|-------|

| BV <sub>DSS</sub>   | Drain-Source Breakdown Voltage   | V <sub>GS</sub> =0V, I <sub>DS</sub> =250μA               | 100  | -    | -    | V     |

| ,                   | Zara Cata Valtaga Prain Current  | V <sub>DS</sub> =80V, V <sub>GS</sub> =0V                 | -    | -    | 1    |       |

| I <sub>DSS</sub>    | Zero Gate Voltage Drain Current  | Т_=85°С                                                   | -    | 1    | 30   | μΑ    |

| I <sub>D</sub>      | Continue Drain Current           | -                                                         | -    | -    | 3    | Α     |

| D                   | Drain-Source On-state Resistance | Vgs=10V, Ips=0.5A                                         | -    | 225  | 325  | mΩ    |

| R <sub>DS(ON)</sub> |                                  | V <sub>GS</sub> =4.5V, I <sub>DS</sub> =0.5A              | -    | 280  | 350  | 11122 |

| $V_{GSS}$           | Gate-Source Breakdown Voltage    | -                                                         | 20   | ı    | 1    | V     |

| I <sub>GSS</sub>    | Gate Leakage Current             | V <sub>GS</sub> =±20V, V <sub>DS</sub> =0V                | -    | -    | ±100 | nA    |

| V <sub>GS(th)</sub> | Gate Threshold Voltage           | V <sub>DS</sub> =V <sub>GS</sub> , I <sub>DS</sub> =250µA | 1    | 1.8  | 2.5  | V     |

| V <sub>SD</sub>     | Diode Forward Voltage            | IDS=0.5A, VGS=0V                                          | -    | 0.7  | 1.3  | V     |

#### **OPERATION**

The FTD1670 is a current mode buck regulator. That is, the EA output voltage is proportional to the peak inductor current. At the beginning of a cycle, M1 is off. The EA output voltage is higher than the current sense amplifier output, and the current comparator's output is low. The rising edge of the 480kHz CLK signal sets the RS Flip-Flop. Its output turns on M1 thus connecting the SW pin and inductor to the input supply.

The increasing inductor current is sensed and amplified by the Current Sense Amplifier. Ramp compensation is summed to the Current Sense Amplifier output and compared to the Error Amplifier output by the PWM Comparator. When the sum of the Current Sense Amplifier output and the Slope Compensation signal exceeds the EA output voltage, the RS Flip-Flop is reset and M1 is turned off. The external Schottky rectifier diode (D1) conducts the inductor current.

If the sum of the Current Sense Amplifier output and the Slope Compensation signal does not exceed the EA output for a whole cycle, then the falling edge of the CLK resets the Flip-Flop.

The output of the Error Amplifier integrates the voltage difference between the feedback and the 0.812V bandgap reference. The polarity is such that lower than 0.812V FB pin voltage increases the EA output voltage. Since the EA output voltage is proportional to the peak inductor current, an increase in its voltage also increases current delivered to the output.

Revision No: 0

## **Application Information**

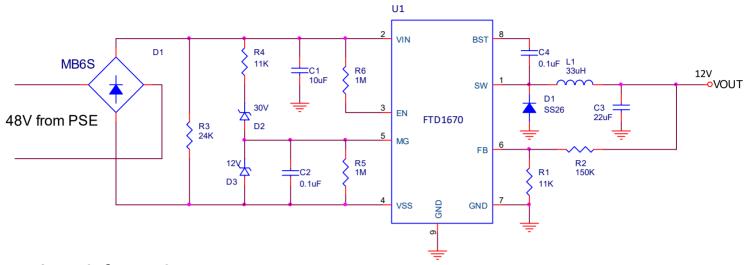

#### **Setting Output Voltage**

The external resistor divider sets the output voltage (see the Typical Application schematic). Table 1 lists resistors for common output voltages. The feedback resistor (R2) also sets the feedback loop bandwidth with the internal compensation capacitor (see Figure 1). R1 is:

$$R1 = \frac{R2}{\frac{V_{OUT}}{0.812V} - 1}$$

Table 1:Resistor Selection for Common output voltages

| VOUT(V) | R1(K Ω ) | R2(K Ω ) |

|---------|----------|----------|

| 1.8     | 102(1%)  | 124(1%)  |

| 2.5     | 59(1%)   | 124(1%)  |

| 3.3     | 40.2(1%) | 124(1%)  |

| 5       | 23.7(1%) | 124(1%)  |

#### **Selecting the Inductor**

Use an inductor with a DC current rating at least 25% percent higher than the maximum load current for most applications. For best efficiency, the inductor's DC resistance should be less than  $200m\Omega$ .

For most designs, the required inductance value can be derived from the following equation.

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_{L} \times f_{SW}}$$

Where  $\Delta I_L$  is the inductor ripple current.

Choose the inductor ripple current to be 30% of the maximum load current. The maximum inductor peak current is:

$$I_{L(MAX)} = I_{LOAD} + \frac{\Delta I_L}{2}$$

Under light-load conditions (below 100mA), use a larger inductance to improve efficiency.

#### **Selecting the Input Capacitor**

The input capacitor reduces the surge current drawn from

the input supply and the switching noise from the device. The input capacitor impedance at the switching frequency should be less than the input source impedance to prevent high-frequency-switching current from passing through the input. Use ceramic capacitors with X5R or X7R dielectrics for their low ESRs and small temperature coefficients. For most applications, a  $4.7\mu F$  capacitor will sufficient.

#### **Selecting the Output Capacitor**

The output capacitor keeps the output voltage ripple small and ensures feedback loop stability. The output capacitor impedance should be low at the switching frequency. Use ceramic capacitors with X5R or X7R dielectrics for their low ESR characteristics. For most applications, a  $22\mu F$  ceramic capacitor will sufficient.

#### **PCB Layout Guide**

PCB layout is very important to stability. Please follow these guidelines and use Figure 2 as reference.

- 1) Keep the path of switching current short and minimize the loop area formed by the input capacitor, high-side MOSFET, and Schottky diode.

- 2) Keep the connection from the power ground→Schottky diode→SW pin as short and wide as possible.

- 3) Ensure all feedback connections are short and direct. Place the feedback resistors and compensation components as close to the chip as possible.

- 4) Route SW away from sensitive analog areas such as FB.

- 5) Connect IN, SW, and especially GND to large copper areas to cool the chip for improved thermal performance and long- term reliability. For single layer PCBs, avoid soldering the exposed pad.

# **Typical Application Circuit**

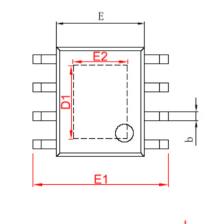

# **Package information**

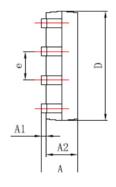

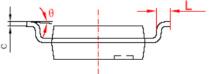

#### **ESOP-8 Package Outline Dimensions**

|    | Dimensions In Millimeters |        | Dimensions | s In Inches |  |

|----|---------------------------|--------|------------|-------------|--|

|    | Min                       | Max    | Min        | Max         |  |

| Α  | 1. 350                    | 1. 750 | 0. 053     | 0.069       |  |

| A1 | 0.050                     | 0. 150 | 0.004      | 0.010       |  |

| A2 | 1. 350                    | 1. 550 | 0. 053     | 0.061       |  |

| b  | 0. 330                    | 0. 510 | 0. 013     | 0. 020      |  |

| С  | 0. 170                    | 0. 250 | 0.006      | 0.010       |  |

| D  | 4. 700                    | 5. 100 | 0. 185     | 0. 200      |  |

| D1 | 3. 202                    | 3. 402 | 0. 126     | 0. 134      |  |

| Е  | 3. 800                    | 4. 000 | 0. 150     | 0. 157      |  |

| E1 | 5. 800                    | 6. 200 | 0. 228     | 0. 244      |  |

| E2 | 2. 313                    | 2. 513 | 0. 091     | 0.099       |  |

| е  | 1. 270 (BSC)              |        | 0.050      | (BSC)       |  |

| L  | 0. 400                    | 1. 270 | 0. 016     | 0.050       |  |

| θ  | 0°                        | 8°     | 0°         | 8°          |  |